信号完整性的设计方法(步骤)

掌握信号完整性问题的相关知识;系统设计阶段采用规避信号完整性风险的设计方案,搭建稳健的系统框架;对目标电路板上的信号进行分类,识别潜在的SI风险,确定SI设计的总体原则;在原理图阶段,按照一定的方法对部分问题提前进行SI设计;PCB布线阶段使用仿真工具量化信号的各项性能指标,制定详细SI设计规则;PCB布线结束后使用仿真工具验证信号电源等网络的各项性能指标,并适当修改。

设计难点信号

质量的各项特征:幅度、噪声、边沿、延时等。SI设计的任务就是识别影响这些特征的因素。难点1:影响信号质量的因素非常多,这些因素有时相互依赖、相互影响、交叉在一起,抑制了某一因素可能会导致其他方面因素的恶化,所有需要对各因素反复权衡,做出系统化的综合考虑;难点2:有些影响信号传输的因素是可控的,而有些是不可控的。 提供完整信号完整性测试解决方案;江苏信号完整性分析安装

数字信号频域分量经过随频率升高损耗加大的传输路径时,接收端收到 的各个频率分量,可以看到,如果这些频率分量要成原来的数字信号的样子,其频谱应 该如虚线所示,而实际上经过传输线后的频谱如实线所示,从而造成信号畸变,从信号眼图 上看眼睛会闭合。

加重(De-Emphasis)和预加重(Pre-Emphasis)的示意图,也就是在发送信 号时降低低频分量或提高高频分量来补偿传输线对不同频率下损耗不一致的影响,使得接收 端的频谱分布和原来想要传输的信号基本一致。 辽宁信号完整性分析参考价格什么是高速电路 高速电路信号完整性分析。

根据上述数据,你就可以选择层叠了。注意,几乎每一个插入其它电路板或者背板的PCB都有厚度要求,而且多数电路板制造商对其可制造的不同类型的层有固定的厚度要求,这将会极大地约束终层叠的数目。你可能很想与制造商紧密合作来定义层叠的数目。应该采用阻抗控制工具为不同层生成目标阻抗范围,务必要考虑到制造商提供的制造允许误差和邻近布线的影响。在信号完整的理想情况下,所有高速节点应该布线在阻抗控制内层(例如带状线)。要使SI比较好并保持电路板去耦,就应该尽可能将接地层/电源层成对布放。如果只能有一对接地层/电源层,你就只有将就了。如果根本就没有电源层,根据定义你可能会遇到SI问题。你还可能遇到这样的情况,即在未定义信号的返回通路之前很难仿真或者仿真电路板的性能。

信号完整性分析三种测试方法

在信号完整性分析中,常用的测试方法包括以下三种:

1.时域测试:时域测试是通过观察信号在时间轴上的波形来分析信号完整性。时域测试可以帮助识别信号的上升时间、下降时间、瞬态响应等参数,从而评估信号是否存在失真。

2.频域测试:频域测试是通过对信号进行傅里叶变换,将信号从时域转换到频域,来分析信号的频率响应。通过分析信号的功率谱密度、带宽等参数,可以评估信号在传输路径中存在的滤波、截止频率等问题。

3.时钟测试:时钟测试是通过观察时钟信号在传输路径中的形状和时间差异来分析时钟信号的完整性。时钟测试可以帮助识别时钟信号的抖动、时钟漂移等问题,从而评估时钟信号是否存在失真。 高速数字电路的信号完整性分析;

边沿时间会影响信号达到翻转门限电平的时间,并决定信号的带宽。

信号之间的偏移(Skew),指一组信号之间的时间偏差,主要是由于在信号之间传输路 径的延时(传输延迟)不同及一组信号的负载不同,以及信号的干扰(串扰)或者同步开关 噪声所造成信号上升下降时间(Rising and Falling Time)的变化等引起的在分析源同步信号时序时需要考虑信号之间的偏移,比如一组DDR数据走线和数据釆样时钟 之间的传输时延的偏差。

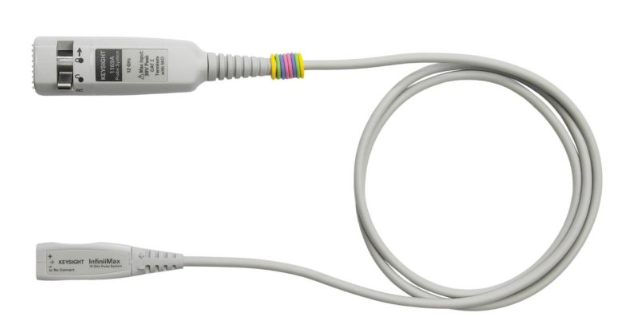

有效高低电平时间(High and Low Times),指信号保证为高或低电平有效的时间,如图 1-15所示。在分析信号时序时必须保证在接收端的数据/地址信号的有效高低电平时间能够满 足接收器件时钟信号判决所需要的建立保持时间的时序要求。 克劳德高速数字信号测试实验室信号完整性使用示波器进行波形测试;辽宁信号完整性分析参考价格

信号完整性分析方法信号完整性分析概述。江苏信号完整性分析安装

信号完整性是许多设计人员在高速数字电路设计中涉及的主要主题之一。信号完整性涉及数字信号波形的质量下降和时序误差,因为信号从发射器传输到接收器会通过封装结构、PCB 走线、通孔、柔性电缆和连接器等互连路径。

当今的高速总线设计如 LpDDR4x、USB 3.2 Gen1/2 (5Gbps/10Gbps)、USB3.2x2 (2x10Gbps)、PCIe 和即将到来的 USB4.0 (2x20Gbps) 在高频数据从发送器流向接收器时会发生信号衰减。本文将概述高速数据速率系统的信号完整性基础知识和集肤效应、阻抗匹配、特性阻抗、反射等关键问题。 江苏信号完整性分析安装

文章来源地址: http://yiqiyibiao.chanpin818.com/zyyqyb/txjcyq/deta_21862513.html

免责声明: 本页面所展现的信息及其他相关推荐信息,均来源于其对应的用户,本网对此不承担任何保证责任。如涉及作品内容、 版权和其他问题,请及时与本网联系,我们将核实后进行删除,本网站对此声明具有最终解释权。

[VIP第1年] 指数:3

[VIP第1年] 指数:3