简单的去加重实现方法是把输出信号延时一个或多个比特后乘以一个加权系数并和 原信号相加。一个实现4阶去加重的简单原理图。

去加重方法实际上压缩了信号直流电平的幅度,去加重的比例越大,信号直流电平被压缩得越厉害,因此去加重的幅度在实际应用中一般很少超过-9.5dB。做完预加重或者去加重的信号,如果在信号的发送端(TX)直接观察,并不是理想的眼图。图1.31所示是在发送端看到的一个带-3.5dB预加重的10Gbps的信号眼图,从中可以看到有明显的“双眼皮”现象。 数字信号常用的编码方式有哪些?安徽USB测试数字信号测试

伪随机码型(PRBS)

在进行数字接口的测试时,有时会用到一些特定的测试码型。比如我们在进行信号质量测试时,如果被测件发送的只是一些规律跳变的码型,可能不了真实通信时的恶劣情况,所以测试时我们会希望被测件发出的数据尽可能地随机以恶劣的情况。同时,因为这种数据流很多时候只是为了测试使用的,用户的被测件在正常工作时还是要根据特定的协议发送真实的数据流,因此产生这种随机数据码流的电路比较好尽可能简单,不要额外占用太多的硬件资源。那么怎么用简单的方法产生尽可能随机一些的数据流输出呢?首先,因为真正随机的码流是很难用简单的电路实现的,所以我们只需要生成尽可能随机的码流就可以了,其中常用的一种数据码流是PRBS(PseudoRandomBinarySequence,伪随机码)码流。PRBS码的产生非常简单,图1.21是PRBS7的产生原理,只需要用到7个移位寄存器和简单的异或门就可以实现。 安徽USB测试数字信号测试数字信号处理系统设计流程;

我们经常使用到的总线根据数据传输方式的不同,可以分为并行总线和串行总线。

并行总线是数字电路中早也是普遍采用的总线结构。在这种总线上,数据线、地址线、控制线等都是并行传输,比如要传输8位的数据宽度,就需要8根数据信号线同时传输;如果要传输32位的数据宽度,就需要32根数据信号线同时传输。除了数据线以外,如果要寻址比较大的地址空间,还需要很多根地址线的组合来不同的地址空间。图1.7是一个典型的微处理器的并行总线的工作时序,其中包含了1根时钟线、16根数据线、16根地址线以及一些读写控制信号。

理想的跳变位置。抖动是个相对的时间量,怎么确定信号的理想的跳变位置对于 抖动的测量结果有很关键的影响。对于时钟信号的测量,我们通常关心的是时钟信号是否 精确地等间隔,因此这个理想位置通常是从被测信号中提取的一个等周期分布时钟的跳变 沿;而对于数据信号的测量,我们关心的是这个信号相对于其时钟的位置跳变,因此这个理 想跳变位置就是其时钟有效沿的跳变位置。对于很多采用嵌入式时钟的高速数字电路来 说,由于没有专门的时钟传输通道,情况要更复杂一些,这时的理想跳变位置通常是指用一 个特定的时钟恢复电路(可能是硬件的也可能是软件的)从数据中恢复出的时钟的有效跳 变沿。什么是数字信号(DigitalSignal);

为了保证接收端在时钟有效沿时采集到正确的数据,通常都有建立/保持时间的要求,以避免采到数据线上跳变时不稳定的状态,因此这种总线对于时钟和数据线间走线长度的差异都有严格要求。这种并行总线在使用中比较大的挑战是当总线时钟速率超过几百MHz后就很难再提高了,因为其很多根并行线很难满图1.15并行总线的时钟传输足此时苛刻的走线等长的要求,特别是当总线上同时挂有多个设备时。为了解决并行总线工作时钟频率很难提高的问题,一些系统和芯片的设计厂商提出了嵌入式时钟的概念。其思路首先是把原来很多根的并行线用一对或多对高速差分线来代替,节省了布线空间;然后把系统的时钟信息通过数据编码的方式嵌在数据流里,省去了专门的时钟走线。信号到了接收端,接收端采用相应的CDR(clock-datarecovery)电路把数据流中内嵌的时钟信息提取出来再对数据采样。图1.16是一个采用嵌入式时钟的总线例子。真实的数字信号频谱;浙江数字信号测试

数字信号处理的解决方案;安徽USB测试数字信号测试

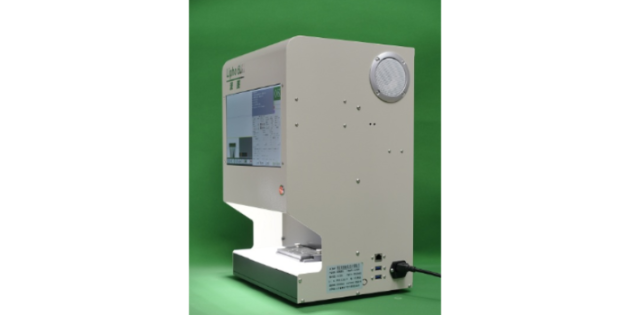

克劳德高速数字信号测试实验室

数字信号测试方法:

需要特别注意,当数字信号的电压介于判决阈值的上限和下限之间时,其逻辑状态是不 确定的状态。所谓的“不确定”是指如果数字信号的电压介于判决阈值的上限和下限之间, 接收端的判决电路有可能把这个状态判决为逻辑0,也有可能判决为逻辑1。这种不确定是 我们不期望的,因此很多数字电路会尽量避免用这种不确定状态进行信号传输,比如会用一 个同步时钟只在信号电平稳定以后再进行采样。

安徽USB测试数字信号测试

文章来源地址: http://yiqiyibiao.chanpin818.com/zyyqyb/txjcyq/deta_21265986.html

免责声明: 本页面所展现的信息及其他相关推荐信息,均来源于其对应的用户,本网对此不承担任何保证责任。如涉及作品内容、 版权和其他问题,请及时与本网联系,我们将核实后进行删除,本网站对此声明具有最终解释权。

[VIP第1年] 指数:3

[VIP第1年] 指数:3